# Capacitance scaling based Thermal Aware Design of Waveform Generator on Virtex-6

Sujeet Pandey<sup>1</sup>, Vivek Kumar Shrivastav<sup>2</sup> <sup>1</sup>Gyancity research lab, Motihari, India <sup>2</sup>Dept of Aerospace Engineering, Indian Institute of Technology, Kharagapur, India <sup>1</sup>welcomesujeet@gmail.com,<sup>2</sup>aerovivek91@gmail.com

**Abstract:** This is an apporach to design of waveform generator on Virtex-6 FPGA that consume low amount of power. we have worked on different value of using capacitance scaling based thermal aware design waveform generator. There is a reduction of 69.10%, 96.77%, 99.56%, and 99.82% in IOs power as the capacitance is scale down from 50000pF to 5000pF, 500pF, 50pF and 5pF respectively.

Keywords: VHDL, FPGA, Energy Efficient, Sinusoidal Waveform Generator.

### **1.INTRODUCTION**

we have design an electrical waveform generator for driving an electromechanical load. This approach consume low amount of power for its operation. Technique applied for doing same is capacitance scaling using Field Programmable gate Array using Xilinx software. For the design of energy efficient we are checking the different level of ambient temperature level and capacitance scaling. We have analyzed the varying the different level of temperature to develop the energy efficient waveform generator. A waveform generator is a piece of electronic test equipment used to generate electrical waveforms. In this paper we have to use Virtex-6 FPGA family to making energy efficient waveform generator. For this model design we have coded in VHDL.

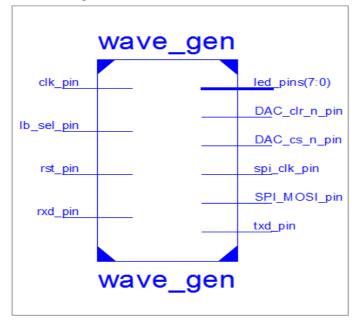

Figure 1 Top Level Schematic of Waveform Generator

## Gyancity Journal of Engineering and Technology, Vol.4, No.1, pp. 1-7, January 2018 ISSN: 2456-0065 DOI: 10.21058/gjet.2018.41001

2

Top level Schematic of Waveform Generator is shown in Figure 1.It has four input port such as clk\_pin, lb\_sel\_pin, rst\_pin, rxd\_pin and six output port such as led pins (7:0), DAC\_clr\_n\_pin, DAC\_cs\_n\_pin, spi\_clk\_pin, SPI\_MOSI\_pin, txd\_pin.

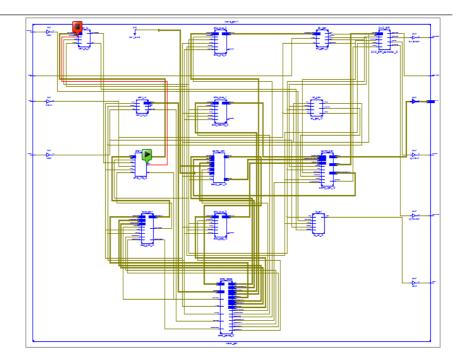

Figure 2 RTL Schematic of Waveform Generator as shown.

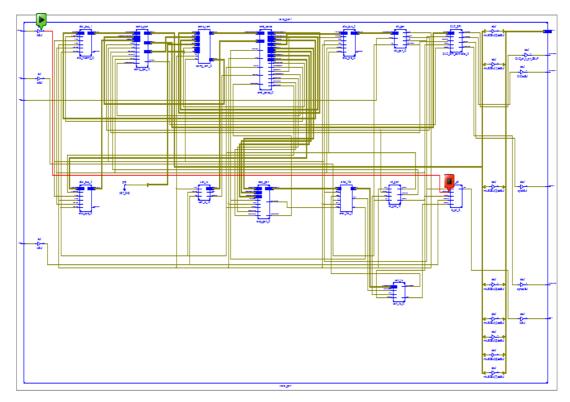

Figure 3 Internal Architecture of Technology Schematic of Waveform Generator.

#### **2. RELATED WORK**

Some researcher has designed low power clock using capacitance scaling [1]. Some of the researcher has done work on Capacitance Scaling Based Low Power Comparator Design on 28nm FPGA [2]. Some researcher has designed FPGA Based Low Power ROM Design Using Capacitance Scaling [3]. Some other researcher has work done on Capacitance scaling based energy efficient FIR filter for digital signal processing [4]. Most of the researcher has done work on the LVTTL IO standards and capacitance scaling based energy efficient ALU design on FPGA [5]. Some author has designed LOTs enable active contour modeling based energy efficient and thermal aware object tracking on FPGA [6]. Some another researcher has work done on Thermal and power aware Internet of Things enable RAM design on FPGA [7]. Some scientists has worked on LVCMOS based thermal aware energy efficient vedic multiplier design on FPGA [8]. Another researcher has done work on Thermal aware low power universal asynchronous receiver transmitter design on FPGA [9]. Some other researcher has done work on the CTHS based energy efficient thermal aware image ALU design on FPGA [10]. In our work we are using different value of capacitance to make energy efficient thermal aware design waveform generator on FPGA.

## **3. RESULTS AND DISCUSSION**

| Capacitance | IOs Power |

|-------------|-----------|

| 5pF         | 0.002     |

| 50pF        | 0.005     |

| 500pF       | 0.037     |

| 5000pF      | 0.355     |

| 50000pF     | 1.149     |

Table 1 IOs Power Dissipation for different capacitance.

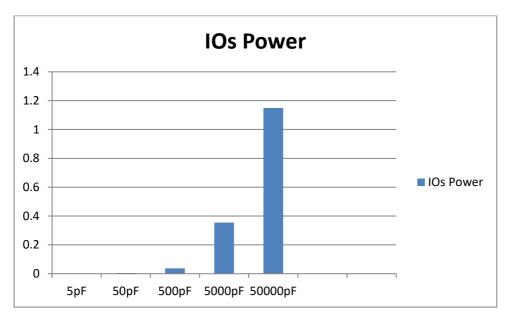

There is a reduction of 69.10%, 96.77%, 99.56%, and 99.82% in IOs power as the capacitance is scale down from 50000pF to 5000pF, 500pF, 50pF and 5pF respectively as shown in Table 1 and Figure 4.

Figure 4 Graph of IOs power of different value of capacitance.

In this paper we can be used for output load capacitance value range from 0pF to 1000000pF but here we have to use up to 50000pF due to junction temperature consideration. After 50000pF junction temperature is too much high. We cannot be considering for life of waveform generator model design.

| Ambient Temperature <sup>oC</sup> | Leakage Power(w) |

|-----------------------------------|------------------|

| 10°C                              | 1.042            |

| 20° <sup>C</sup>                  | 1.093            |

| 30°C                              | 1.152            |

| 40°C                              | 1.219            |

| 50°C                              | 1.295            |

Table 2 Leakage power on different value of ambient temperature.

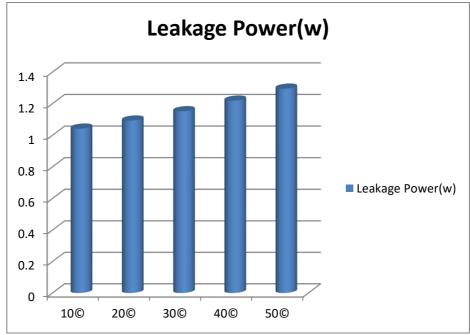

There is a reduction of 05.86%, 11.04%, 15.59%, 19.53% in IOs power as the capacitance is scale down from  $50^{\circ C}$  to  $40^{\circ C}$ ,  $30^{\circ C}$ ,  $20^{\circ C}$  and  $10^{\circ C}$  respectively as shown in Table 2 and Fig.5.

Figure 5 Graph of leakage power of different value of ambient temperature.

In this graph we have to see that slightly increase in leakage power from 1.042, 1.093, 1.152, 1.219, 1.295 with increase in ambient temperature from  $10^{\circ C}$  to  $50^{\circ C}$  respectively. So, ambient temperature is directly proportional to leakage power. It is nonlinear function. If temperature is increases leakage will be increase and vice-versa.

| ~             |

|---------------|

| <b>`</b>      |

| $\mathcal{I}$ |

| Ambient                   | clocks | logic | signals | BRAMs | MMCMs |

|---------------------------|--------|-------|---------|-------|-------|

| Temperature <sup>oC</sup> |        |       |         |       |       |

| 10 <sup>oC</sup>          | 0.016  | 0.003 | 0.002   | 0.003 | 0.083 |

| 20 <sup>oC</sup>          | 0.016  | 0.003 | 0.002   | 0.003 | 0.083 |

| 30 <sup>oC</sup>          | 0.016  | 0.003 | 0.002   | 0.003 | 0.083 |

| $40^{\text{oC}}$          | 0.016  | 0.003 | 0.002   | 0.003 | 0.083 |

| $50^{\mathrm{oC}}$        | 0.016  | 0.003 | 0.002   | 0.003 | 0.083 |

Table 3 Different power dissipation when clock pulse period is 10 ns.

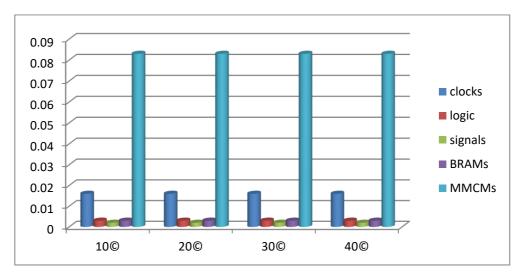

There is no change in clocks, logic, signals, BRAMs, MMCMs power when ambient temperature is changes from  $10^{\circ C}$  to  $50^{\circ C}$  as shown in table 3 and fig.6. It is a constant value for any value of ambient temperature. So, there is no effect of temperature on clocks, logic, signals, BRAMs, MMCMs power. For any value of temperature clocks, logic, signals, BRAMs, MMCMs power is 0.016, 0.003, 0.002, 0.003, and 0.083 respectively.

Figure 6 Graph of different power when clock pulse period is 10ns.

Here in graph we have to see that there is no change in all type of power if ambient temperature is changes from  $10^{\circ C}$  to  $50^{\circ C}$ .

| Device Utilization Summary (estimated values) [-] |      |           |             |  |  |  |  |

|---------------------------------------------------|------|-----------|-------------|--|--|--|--|

| Logic Utilization                                 | Used | Available | Utilization |  |  |  |  |

| Number of Slice Registers                         | 574  | 93120     | 0%          |  |  |  |  |

| Number of Slice LUTs                              | 892  | 46560     | 1%          |  |  |  |  |

| Number of fully used LUT-FF pairs                 | 262  | 1204      | 21%         |  |  |  |  |

| Number of bonded IOBs                             | 16   | 240       | 6%          |  |  |  |  |

| Number of Block RAM/FIFO                          | 1    | 156       | 0%          |  |  |  |  |

| Number of BUFG/BUFGCTRLs                          | 3    | 32        | 9%          |  |  |  |  |

Here we have seen that logic utilization is negligible for number of slice Registers available. It is used 574 out of 93120 Available for it. and number of slice LUTs utilization is very less value only 1%. Number of block RAM/FIFO utilization is negligible only 1 out of 156 available.

## **4. CONCLUSION**

Here, we have concluded that there is noticeable change by varying output load at different value of capacitance and ambient temperature changes using low power Virtex-6 FPGA. Work is done in order to have an efficient design. This will help in designing low power waveform generator for efficient output.Virtex-6 gives low power readings and so is efficient for designing of not 0nly for waveform generator but various electronic designs. The capacitance scaling used from 5pF to 50000pF for clock pulse period is 10ns.

## **5. FUTURE SCOPE**

This waveform generator model will be energy efficient and hence saves energy and power. In future we can be uses for different approaches can be made to efficient better than this. Different FPGA families like Spartan-6, Kintex-7, Airtex-7 etc. can be used for different standards like HSTL, DDR, LVCMOS, SSTL and PCI33\_3 [9] etc. we have to use Frequency Scaling can also be done in future instead of varying the output load to save the energy and power.

### REFERENCES

- [1]. Gargrish, S., Kaur, H., & Tanwar, P. (2014). Implementation of Low Power Digital Clock Design Using Capacitance Scaling On FPGA.

- [2]. Saxena, A., Gaidhani, S., Pant, A., & Patel, C. (2015). Capacitance Scaling Based Low Power Comparator Design on 28nm FPGA. *International Journal of Computer Trends and Technology* (*IJCTT*)–Volume X Issue Y-Month.

- [3]. Bansal, M., Bansal, N., Saini, R., Kalra, L., Mohan Singh, P., Pandey, B., & Akbar Hussain, D. M. (2015). FPGA Based Low Power ROM Design Using Capacitance Scaling. In *Advanced Materials Research* (Vol. 1082, pp. 471-474). Trans Tech Publications.

- [4]. Pandey, B., Kumar, T., Das, T., Yadav, R., & Pandey, O. J. (2014, February). Capacitance scaling based energy efficient FIR filter for digital signal processing. In *Optimization, Reliability, and Information Technology (ICROIT), 2014 International Conference on* (pp. 448-451). IEEE.

- [5]. Kumar, T., Kumar, P., Chowdhry, B. S., & Pandey, B. (2014). LVTTL IO standards and capacitance scaling based energy efficient ALU design on FPGA. *Ned University Journal of Research*, 39.

- [6]. Musavi, S. H. A., Chowdhry, B. S., Kumar, T., Pandey, B., & Kumar, W. (2015). IoTs enable active contour modeling based energy efficient and thermal aware object tracking on FPGA. *Wireless Personal Communications*, 85(2), 529-543.

- [7]. Verma, G., Moudgil, A., Garg, K., & Pandey, B. (2015, March). Thermal and power aware Internet of Things enable RAM design on FPGA. In *Computing for Sustainable Global Development (INDIACom), 2015 2nd International Conference on* (pp. 1537-1540). IEEE.

- [8]. Goswami, K., & Pandey, B. (2014, November). LVCMOS based thermal aware energy efficient vedic multiplier design on FPGA. In *Computational Intelligence and Communication Networks* (*CICN*), 2014 International Conference on (pp. 921-924). IEEE.

- [9]. Singh, S., Jain, A., Kaur, A., & Pandey, B. (2014, November). Thermal aware low power universal asynchronous receiver transmitter design on FPGA. In *Computational Intelligence and Communication Networks (CICN), 2014 International Conference on* (pp. 939-942). IEEE.

[10]. Kumar, T., Pandey, B., Mussavi, S. H. A., & Zaman, N. (2015). CTHS based energy efficient thermal aware image ALU design on FPGA. *Wireless Personal Communications*, 85(3), 671-696.